# Enpirion® Power Datasheet EC2630QI 4.5A, 27W 12V DC-DC Intermediate Voltage Bus Converter

## Description

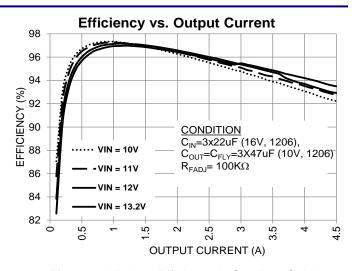

The EC2630QI is a high density, high efficiency DC-DC intermediate voltage bus converter which generates an output voltage that tracks one half the input voltages and is designed to provide power to Altera's highly integrated Enpirion DC-DC point-of-load converter products for a complete 12V solution. EC2630QI provides the means to condition power from a 12V input, to supply multiple lower voltage converters while enabling high efficiency and small PCB area. Due to its extremely high efficiency, it avoids the common two stage power conversion penalty and is equivalent to or better than direct regulation.

This Altera Enpirion solution significantly helps in system design and productivity by offering greatly simplified board design, layout and manufacturing. In addition, a reduction in the number of vendors required for the complete power solution helps to enable an overall system cost savings. All of Altera's Enpirion products are RoHS compliant.

#### **Features**

- Complete power conditioning solution from a 12 volt power bus.

- 5.5mm x 5.5mm x 3mm QFN Package.

- Total solution size of 228mm<sup>2</sup>.

- Input voltage range of 10V to 13.2V.

- The output voltage is half the input voltage.

- High and flat efficiency, up to 97.5%.

- 4.5A Continuous Output Current Capability.

- Adjustable operating frequency with optional external clock input.

- Master/Slave Mode for Parallel Operation.

- Output VIN\_OK pin.

- Thermal shutdown, short circuit, Overcurrent, and UVLO protection.

- RoHS compliant, MSL level 3, 260C reflow.

#### **Applications**

- Applications requiring down conversion from a 12V bus to an output voltage with high efficiency.

- Systems requiring multiple voltage rails such as FPGA and ASIC.

- Enterprise, Industrial, Embedded, and Telecommunication applications.

- Multi-rail computer & network interface applications such as PCIe and ATCA AMC cards.

- 12V Industrial and Consumer Applications such

- as Audio/Video Home Theater, Tuners

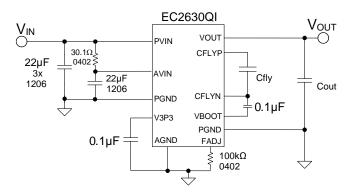

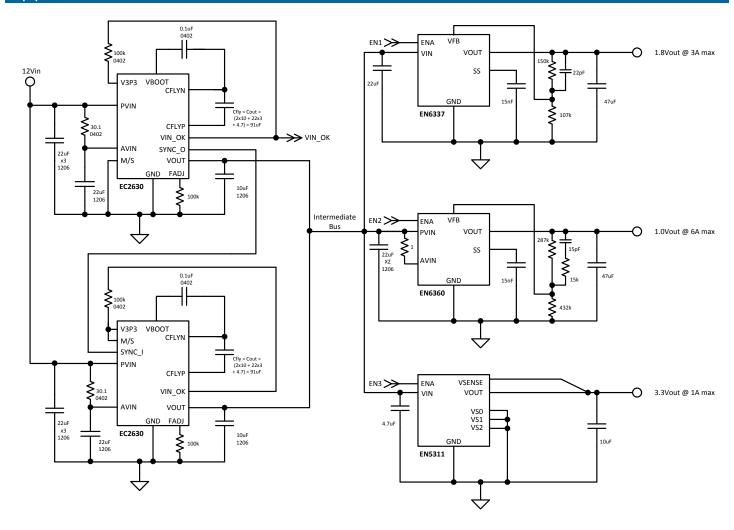

Figure 1. Typical Application Schematic Optimized for Maximum Efficiency

**Figure 2.** Highest Efficiency in Smallest Solution Size

## Ordering Information

| Part Number  | Package Markings | T <sub>AMBIENT</sub> Rating (°C) | Package Description                      |  |  |

|--------------|------------------|----------------------------------|------------------------------------------|--|--|

| EC2630QI     | EC2630QI         | -40 to +85                       | 36 pin (5.5mm x 5.5mm x 3mm) QFN Package |  |  |

| EVB-EC2630QI | EC2630QI         | QFN Evaluation Board             |                                          |  |  |

Packing and Marking Information: <a href="https://www.altera.com/support/reliability/packing/rel-packing-and-marking.html">www.altera.com/support/reliability/packing/rel-packing-and-marking.html</a>

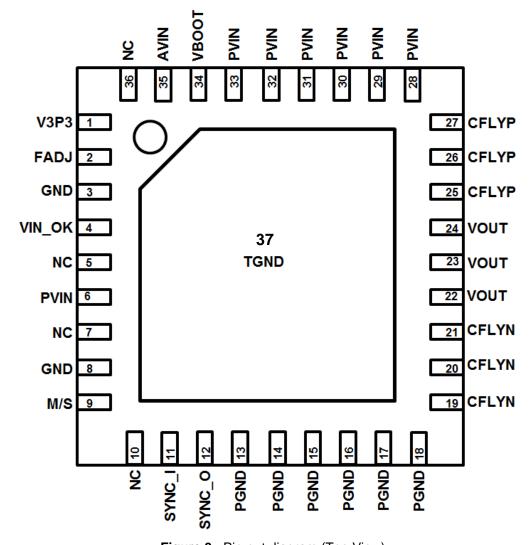

#### Pin Assignments (Top View)

Figure 3. Pin-out diagram (Top View)

**NOTE A**: NC pins are not to be electrically connected to each other or to any external signal, ground, or voltage. Failure to follow this guideline may result in damage to the device.

**NOTE B**: The white dot on the top left of the device package is the pin-1 indicator.

# Pin Descriptions

| I/O Legend | d: P=Powe | r   | G=Ground NC=No Connect I=Input O=Output I/O=Input/outp |                                                                                  | I/O=Input/output             |                            |  |  |  |

|------------|-----------|-----|--------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------|----------------------------|--|--|--|

| PIN        | NAME      | I/O |                                                        |                                                                                  | FUNCTION                     |                            |  |  |  |

| 1          | V3P3      | 0   | Internal Reg                                           | nternal Regulated Supply Output. Connect bypass capacitor from V3P3 to GND.      |                              |                            |  |  |  |

| 2          | FADJ      | I/O | Frequency A                                            | requency Adjust pin used to set the switching frequency. See Theory of Operation |                              |                            |  |  |  |

|            |           |     |                                                        | selecting the required re                                                        |                              |                            |  |  |  |

| 3, 8       | GND       | G   |                                                        |                                                                                  | d. Must tie directly to grou | und plane with a via right |  |  |  |

|            |           |     | next to each                                           |                                                                                  |                              |                            |  |  |  |

| 4          | VIN_OK    | 0   |                                                        |                                                                                  | tem state indication for no  |                            |  |  |  |

|            |           |     |                                                        |                                                                                  | reater than 9V. This pin ca  |                            |  |  |  |

|            |           |     |                                                        |                                                                                  | nverters powered by the I    |                            |  |  |  |

| 5, 7,      | NC        | NC  |                                                        |                                                                                  | connect these pins to ea     | ich other or to any other  |  |  |  |

| 10, 36     |           |     |                                                        | nal. CAUTION: May b                                                              | e internally connected.      |                            |  |  |  |

| 6          | PVIN      | Р   | Main Input S                                           | 117                                                                              |                              |                            |  |  |  |

| 9          | M/S       | I   |                                                        |                                                                                  | nization. Logic low = Mas    | ter. Logic high = Slave.   |  |  |  |

|            |           |     |                                                        | er mode for standalone                                                           |                              |                            |  |  |  |

| 11         | SYNC_I    | I   |                                                        |                                                                                  | , input accepted in Slave    |                            |  |  |  |

|            |           |     |                                                        |                                                                                  | left floating when used in   |                            |  |  |  |

| 12         | SYNC_O    | 0   |                                                        |                                                                                  | des clock input to EC2630    | s in slave mode.           |  |  |  |

| 13-18      | PGND      | G   |                                                        | nd for the switching vol                                                         |                              |                            |  |  |  |

| 19-21      | CFLYN     | I/O |                                                        | rminal of Flying Capac                                                           | tor                          |                            |  |  |  |

| 22-24      | VOUT      | 0   |                                                        | utput Voltage                                                                    |                              |                            |  |  |  |

| 25-27      | CFLYP     | I/O |                                                        | minal of Flying Capacit                                                          | or                           |                            |  |  |  |

| 28-33      | PVIN      | Р   | Main Input S                                           | Supply                                                                           |                              |                            |  |  |  |

| 34         | VBOOT     | I/O | Internal pow                                           | er Supply for high-side                                                          | drive. Connect a 0.1uF/2     | 5V boot-strap capacitor    |  |  |  |

|            |           |     | from VBOO                                              | Γ to CFLYN.                                                                      |                              |                            |  |  |  |

| 35         | AVIN      | Р   | Quiet Input                                            | Supply for Controller. C                                                         | onnect to PVIN through a     | n RC filter. Refer to      |  |  |  |

|            |           |     | application s                                          | schematics for details                                                           |                              |                            |  |  |  |

| 37         | TGND      | G   | This pad is a                                          | a thermal ground. It mu                                                          | st be thermally and electri  | ically connected to the    |  |  |  |

|            |           |     | ground plan                                            | e through a matrix of vi                                                         | as.                          |                            |  |  |  |

# Absolute Maximum Ratings

**CAUTION**: Absolute Maximum ratings are stress ratings only. Functional operation beyond recommended operating conditions is not implied. Stress beyond absolute maximum ratings may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

| PARAMETER                                              | SYMBOL                 | MIN  | MAX     | UNITS |

|--------------------------------------------------------|------------------------|------|---------|-------|

| Input Supply Voltage – PVIN, AVIN                      | $V_{IN}$               | -0.5 | 13.5    | V     |

| Input Voltage – VIN_OK, CFLYN, CFLYP, Vout             |                        | -0.5 | VIN     | V     |

| Input Voltage - V3P3, FADJ, M_S, SYNC_I, SYNC_O        |                        | -0.5 | 3.5     | V     |

| Input Voltage – VBOOT                                  |                        | -0.5 | VIN + 8 | V     |

| Storage Temperature Range                              | T <sub>STG</sub>       | -65  | 150     | °C    |

| Maximum Operating Junction Temperature                 | T <sub>J-ABS MAX</sub> |      | 150     | °C    |

| Reflow Temp, 10 Sec, MSL3 JEDEC J-STD-020A             |                        |      | 260     | °C    |

| ESD Rating (based on Human Body Model): AVIN           | Positive               | 1500 |         | V     |

|                                                        | Negative               | 2000 |         |       |

| ESD Rating (based on Human Body Model): All other pins |                        | 2000 |         | V     |

| ESD Rating (based on Charged Device Model)             |                        | 500  |         | V     |

# Recommended Operating Conditions

| PARAMETER                      | SYMBOL               | MIN | TYP | MAX  | UNITS |

|--------------------------------|----------------------|-----|-----|------|-------|

| Input Voltage Range            | V <sub>IN</sub>      | 10  | 12  | 13.2 | V     |

| Continuous Output Current      | I <sub>OUT_MAX</sub> |     |     | 4.5  | А     |

| Operating Junction Temperature | T <sub>J</sub>       | -40 |     | +125 | °C    |

# Thermal Characteristics

| PARAMETER                               | SYMBOL            | MIN | TYP | MAX | UNITS |

|-----------------------------------------|-------------------|-----|-----|-----|-------|

| Thermal Shutdown                        | T <sub>SD</sub>   |     | 155 |     | °C    |

| Thermal Shutdown Hysteresis             | T <sub>SDH</sub>  |     | 25  |     | °C    |

| Thermal Resistance: Junction to Case    | $\theta_{\sf JC}$ |     | 1   |     | °C/W  |

| Thermal Resistance: Junction to Ambient | $\theta_{JA}$     |     | 19  |     | °C/W  |

#### Electrical Characteristics

NOTE:  $V_{IN}$ =12.0V over operating temperature range unless otherwise noted. Typical values are at  $T_A$  = 25°C.

| PARAMETER                                       | SYMBOL            | <b>TEST CONDITIONS</b>                                                 | MIN          | TYP  | MAX           | UNITS |

|-------------------------------------------------|-------------------|------------------------------------------------------------------------|--------------|------|---------------|-------|

| Operating Boot Strap<br>Voltage                 | VBOOT             | @ Vin =12V, with 0.1uF capacitor between VBOOT and CFLYN               |              | 17   |               | V     |

| Internal Regulated Supply Output                | V3P3              | @ Vin =12V                                                             | 2.97         | 3.3  | 3.63          | V     |

| Input under Voltage<br>Lockout                  | $V_{\text{UVLO}}$ |                                                                        | 4.5          | 5    | 5.5           | V     |

| Input Voltage Indication Rising                 | VIN_OK            |                                                                        | 8            | 9    | 10            | V     |

| Input Voltage Indication Falling                | VIN_OK            |                                                                        | 7            | 8    | 9             | V     |

| No-Load Operating Current                       | I <sub>OP</sub>   | @ 12V input and 125kHz switching                                       |              | 16   |               | mA    |

| Switching Frequency<br>(Internal Oscillator)    | Fosc              | $R_{FADJ}$ = 100 K $\Omega$ ,                                          | 68           | 115  | 165           | kHz   |

| Frequency Adjust Voltage                        | $V_{FADJ}$        |                                                                        |              | 1.2  |               | V     |

| Output Voltage as a fraction of input voltage 1 | V <sub>OUT</sub>  | $10V \le V_{IN} \le 13.2V,$ $0A \le I_{LOAD} \le 4A$                   | 45           |      | 50            | %     |

| Output Impedance                                | R <sub>OUT</sub>  | $\Delta V_{OUT}/\Delta I_{LOAD}$<br>$R_{FADJ} = 100 \text{ K}\Omega$ , |              | 90   |               | mΩ    |

| Overcurrent Trip Level                          | V <sub>OCP</sub>  | Vin=12V. Overcurrent sensed as a drop in output voltage                |              | 5.2  |               | V     |

| M_S input Logic Low                             | M_S_I_VIL         |                                                                        | -0.3         |      | 0.3           | V     |

| M_S input Logic High                            | M_S_I_VIH         |                                                                        | V3P3-<br>0.6 | V3P3 | V3P3 +<br>0.3 | V     |

| Clock Input Logic Low                           | SYNC_I_VIL        |                                                                        |              |      | 0.3           | V     |

| Clock Input Logic High                          | SYNC_I_VIH        |                                                                        | 1.8          |      | 3.3           | V     |

| Clock Output Logic Low                          | SYNC_O_VOL        |                                                                        |              |      | 0.3           | V     |

| Clock Output Logic High                         | SYNC_O_VOH        | @ 1mA                                                                  | V3P3-<br>0.6 |      |               | V     |

<sup>&</sup>lt;sup>1</sup> Altera recommends that Cfly=Cout.

| PARAMETER               | SYMBOL            | TEST CONDITIONS                                                                               | MIN | TYP   | MAX | UNITS |

|-------------------------|-------------------|-----------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| VIN_OK, sink capability |                   |                                                                                               |     | 1     |     | mA    |

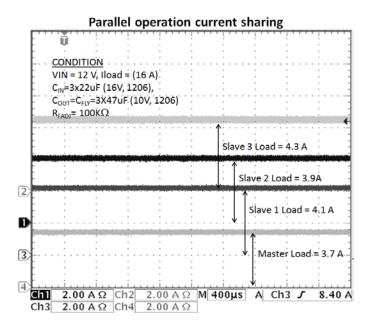

| Current Balance         | ΔΙ <sub>Ουτ</sub> | With 2 to 4 Converters in Parallel, the Difference Between Nominal and Actual Current Levels. |     | +/-10 |     | %     |

## Typical Performance Curves

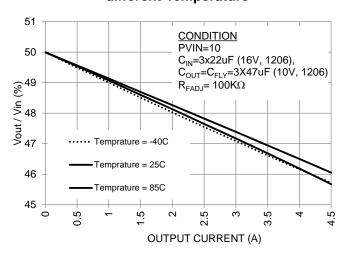

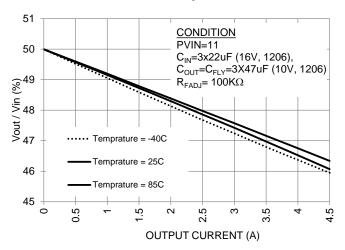

# Output Voltage as a fraction of VIN at different Temperature

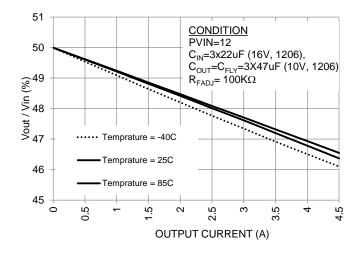

# Output Voltage as a fraction of VIN at different Temperature

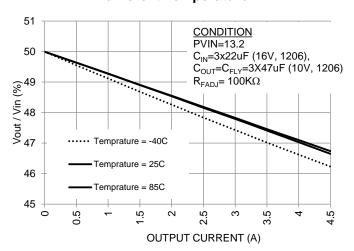

# Output Voltage as a fraction of VIN at different Temperature

# Output Voltage as a fraction of VIN at different Temperature

05996

**OUTPUT CURRENT (A)**

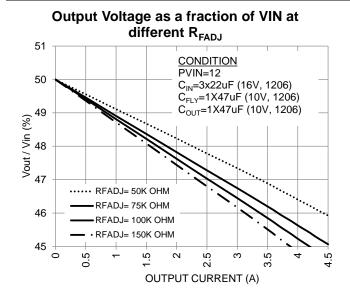

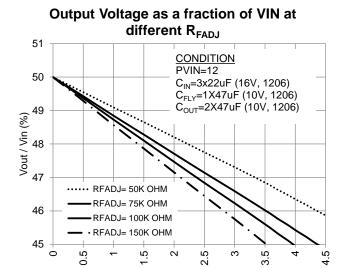

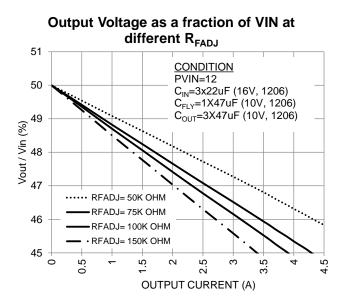

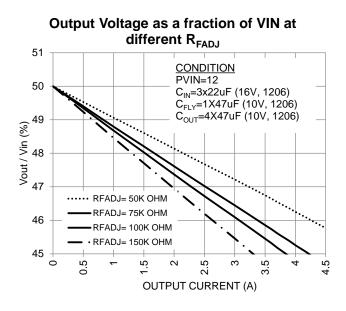

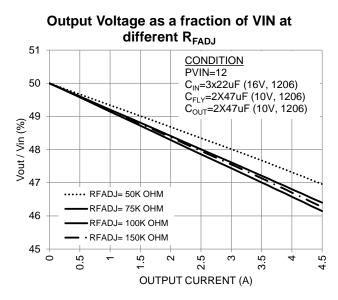

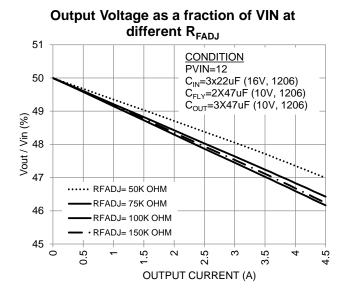

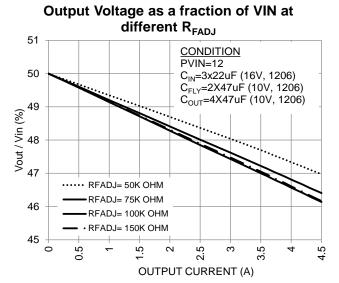

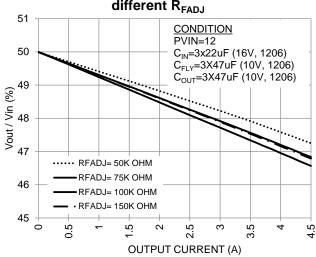

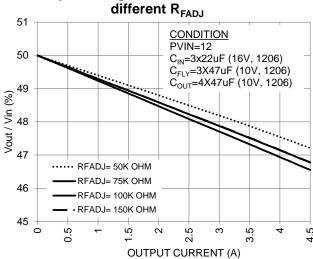

# Output Voltage as a fraction of VIN at different R<sub>FADJ</sub>

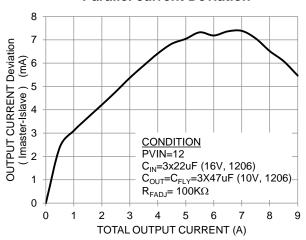

#### **Parallel current Deviation**

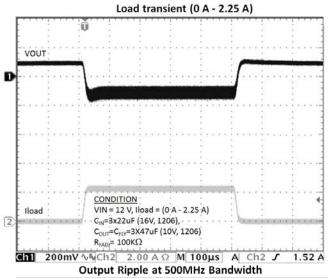

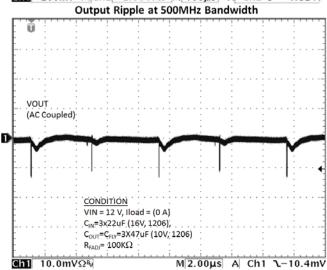

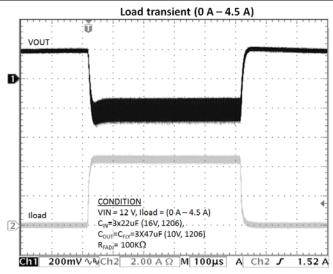

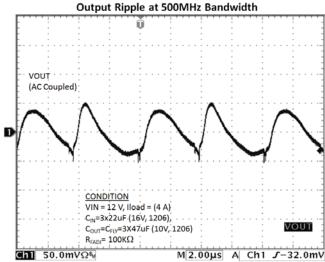

## **Typical Performance Characteristics**

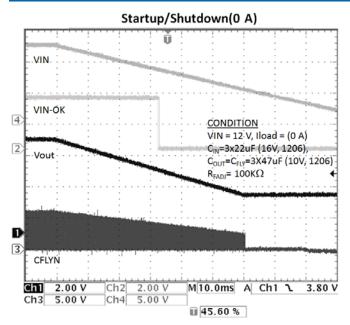

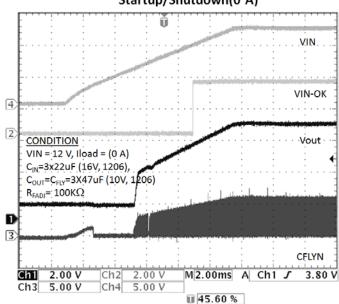

#### Startup/Shutdown(0 A)

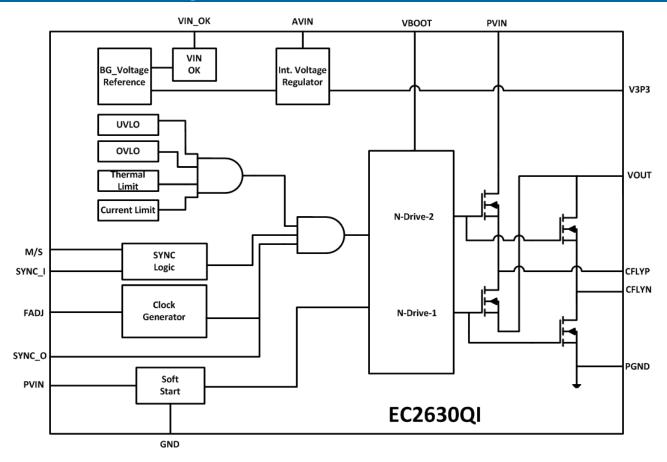

## Functional Block Diagram

Figure 4. Functional Block Diagram

### Theory of Operation

#### **Bus Voltage Divider**

The EC2630QI is an open loop voltage divider. It generates an output voltage which is approximately half the input voltage value. The device uses switched capacitors to divide the input voltage by a factor of 2. External capacitors are charged in series during one half of a clock cycle and the capacitors are then connected in parallel during the second half of the clock cycle. The output voltage depends on the input voltage and the load current.

This device has been designed specifically for use with Altera's Enpirion point-of-load products for output voltage regulation.

The Voltage Divider has the following features:

- Over-current protection (to protect the IC from excessive load current)

- Thermal shutdown with hysteresis.

- Under-voltage lockout circuit to disable the converter output when the input voltage is less than approximately 5V.

- Switching frequency is internally generated.

- However, a clock signal from a Master EC2630QI may be applied externally when the device is configured in Slave mode.

- When in Master mode, the device will output its internal clock to the SYNC\_O pin.

- Soft-start circuit, to limit the in-rush current when the converter is powered up.

- VIN\_OK indicator signal.

#### Frequency Synch (Master/Slave)

In Master mode, the internal switching frequency of the Master device is output through SYNC\_O pin. This clock signal can be used to drive other EC2630QI devices for synchronization or parallel operation. In Slave mode, a master device's SYNC\_O pin provides the clock input by connecting it to the slave device's SNYC\_I pin. Note that in order for the device to function properly in slave mode, it has to be clocked from a valid EC2630QI master device. Applying an external signal/clock to the SYNC\_I pin might cause unpredicted operation and potentially damage the device.

#### **Soft-Start Operation**

Soft start is a means to reduce the in-rush current when the device is enabled.

When the device is enabled by ramping up the input voltage, and the output capacitors are discharged, a large current flow is averted by modulating the gate drive of the NFET during the soft start interval. This interval is pre-programmed and not user programmable.

#### **Overcurrent Protection**

The overcurrent function is achieved by sensing the output voltage. An overcurrent state is entered when the device is out of soft start and the output voltage drops below ~85% of the expected voltage. This overcurrent state will initiate a fresh soft-start and the device will continue cycling through soft-start as long as the overcurrent condition exists. Note that the over current protection level is dependent on the switching frequency and the output capacitance. From the below table, we can

Note that the over current protection level is dependent on the switching frequency and the output capacitance. From the below table, we can achieve a lower over current protection level by decreasing the switching frequency or the output capacitance.

|                   |      | OCP  | Level |      |

|-------------------|------|------|-------|------|

| R <sub>FADJ</sub> | 100K | 150K | 200K  | 250K |

|                   |      |      |       |      |

| Cout=Cfly         |      |      |       |      |

| 1x47 uF           | 5.5  | 4.3  | 2.9   | 2.9  |

| 2x47 uF           | 8.4  | 7    | 4.7   | 4.8  |

| 3x47 uF           | 9    | 8.6  | 6.6   | 5.9  |

| 4x47 uF           | 10.5 | 9.5  | 7.5   | 6.7  |

Altera has observed that current conditions over 6A while VOUT is regulating at VIN/2 can lead to device failure.

#### Thermal Overload Protection

Thermal shutdown will disable operation when the Junction temperature exceeds the value given in

the Thermal Characteristics table. Once the junction temperature drops by the hysteresis temperature, the converter will re-start with a normal soft-start.

#### Input Under-voltage Lock-out

Internal circuits ensure that the converter will not start switching until the input voltage is above the specified minimum voltage of ~5V. If the voltage drops below the UVLO threshold the lockout circuitry will again disable the switching. Hysteresis is included to prevent chattering between states.

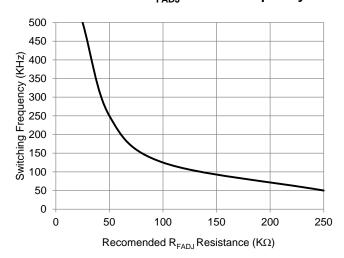

#### **Frequency Adjustment**

The device is optimized to run at 125 kHz switching frequency (with  $R_{\text{FADJ}}$ = 100 k $\Omega$ ) independent of load current. The internal oscillator frequency can be adjusted by altering the value of the resistor between the FADJ pin and AGND (see chart below).

#### Recomended R<sub>FADJ</sub> vs. SW Frequency

Figure 5. Recommended R<sub>FADJ</sub> vs. switching frequency

# Capacitor Selection

The EC2630QI requires a range of capacitance depending on application configuration. Capacitor selection is dependent upon power level, efficiency, space, and cost requirements. Low-cost, low-ESR X5R or X7R ceramic capacitors should be used. Either 1206 or 1210 case sizes are recommended. In general, 1210 capacitors exhibit less voltage coefficient than 1206 capacitors, providing more

capacitance per unit volume-volt. Y5V or equivalent dielectric formulations must not be used as they lose capacitance with frequency, temperature and bias voltage.

#### Output capacitor and fly capacitor consideration:

Altera recommends that the Cfly value is roughly matched to the value of Cout. Note that except where indicated otherwise, the guaranteed values

and charts provided in the datasheet, including the ones for load regulation, hold good only under this condition (Cout=Cfly). For applications where there is a large mismatch between Cfly and Cout, the curves relating output voltage to Cout/Cfly ratio over load and frequency (provided in the Typical Performance Curves section) may be used to predict device operation.

Capacitor selection guidelines to support full output load (4.5A):

#### Input Capacitors-

A typical implementation might use 3x22μF, 16V 1206, MLCC capacitors

#### Output Capacitors-

As EC2630 is used to power up downstream Altera Enpirion point-of-load (POL) converters, the input capacitors for the downstream POL converters are the output capacitors for the EC2630QI. It only requires an additional local output capacitor (1x10µF). Wherever possible, it is recommended to have the downstream converters close to the bus converter.

- The minimum implementation for output capacitor (10μF local cap + the input caps for the downstream POL) might use (1X47μF + 1x10μF), 10V, and 1206 output.

- The maximum implementation might use (4X47µF), 10V, and 1206 output.

#### Flying Capacitors-

Flying capacitors are approximately equal to the output capacitors, and a typical implementation might use 3x47µF, 10V, and 1206.

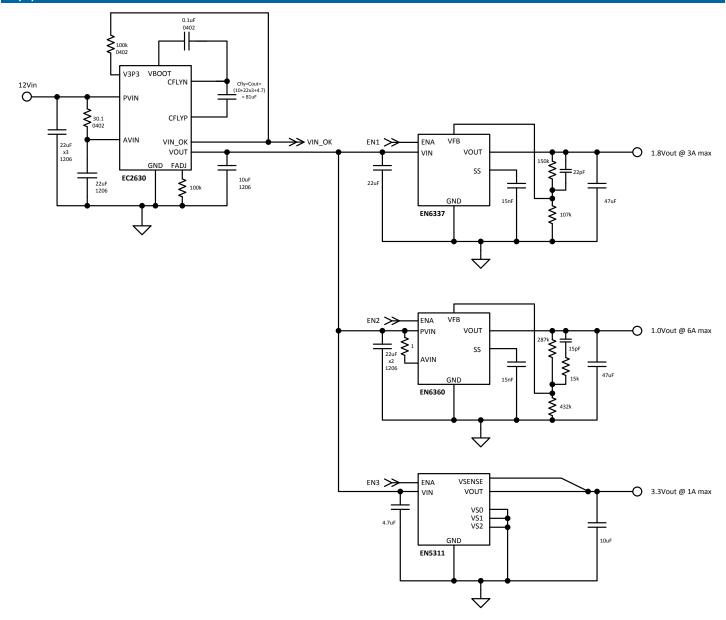

## Application Schematic

Figure 6. EC2630 connected to a 12V input supplying 3 point-of-load Altera Enpirion DC-DC switchers

Figure 6 shows a typical application where the EC2630 is powering up three downstream Altera Enpirion point-of-load (POL) converters. The EC2630 VIN\_OK signal, along with a sequencer if necessary, is used to control the ENABLE pins of the downstream devices based on the application's sequencing requirements. The sequencing has to ensure that the intermediate bus voltage is up before the POL converters start switching. In addition, it is recommended to use only Altera's Enpirion POL converters rated for up to 6.6V input voltage operation as downstream devices.

**NOTE:** The V3P3 supply is meant to power only internal circuitry, apart from a pull-up resistor to VIN\_OK. Altera recommends a  $100k\Omega$  pull-up resistor to V3P3 for most applications. Do not connect multiple pull-ups to the V3P3 pin.

# Application Schematic

Figure 7. Parallel operation with two EC2630 devices

Figure 7 shows parallel operation of two EC2630 devices. The Master and Slave operate at a synchronized clock frequency, provided by the master through its SYNC\_O pin. For parallel operation, no more than four parallel devices are recommended to ensure there are no significant voltage drops between the input supply and any of the paralleled devices.

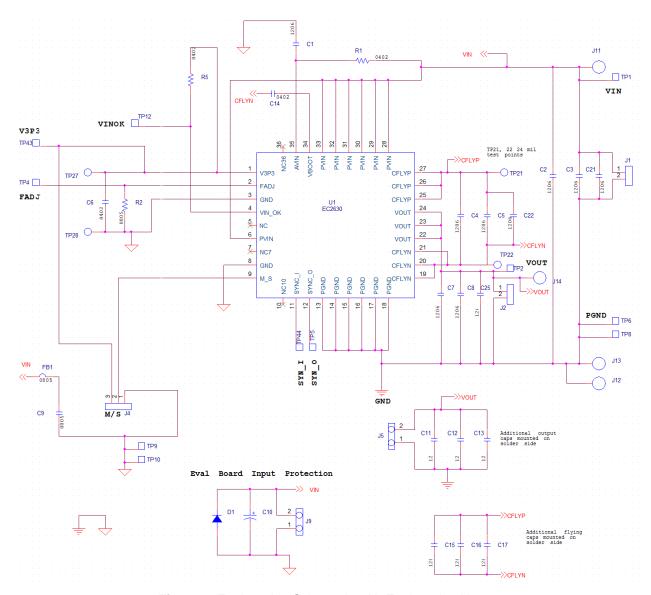

# **Engineering Schematic**

Figure 8. Engineering Schematic with Engineering Notes

## Layout Recommendations

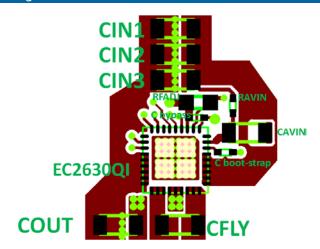

**Figure 9.** Top Layout with Critical Components Only (Top View). See Figure 8 for corresponding schematic

This layout only shows the critical components and top layer traces for minimum footprint. Alternate circuit configurations & other low-power pins need to be connected and routed according to customer application. Please see the Gerber files at <a href="www.altera.com/enpirion">www.altera.com/enpirion</a> for details on all layers.

**Recommendation 1:** Input and output filter capacitors should be placed on the same side of the PCB, and as close to the EC2630QI package as possible. They should be connected to the device with very short and wide traces. Do not use thermal reliefs or spokes when connecting the capacitor pads to the respective nodes. The +V and GND traces between the capacitors and the EC2630QI should be as close to each other as possible so that the gap between the two nodes is minimized, even under the capacitors.

**Recommendation 2:** The PGND connections for the input and output capacitors on layer 1 need to have a

slit between them in order to provide some separation between input and output current loops.

**Recommendation 3:** The system ground plane should be the first layer immediately below the surface layer. This ground plane should be continuous and un-interrupted below the converter and the input/output capacitors.

**Recommendation 4**: The thermal pad underneath the component must be connected to the system ground plane through as many vias as possible. The drill diameter of the vias should be 0.33mm, and the vias must have at least 1 oz. copper plating on the inside wall, making the finished hole size around 0.20-0.26mm. Do not use thermal reliefs or spokes to connect the vias to the ground plane. This connection provides the path for heat dissipation from the converter.

**Recommendation 5**: Multiple small vias (the same size as the thermal vias discussed in recommendation 4) should be used to connect ground terminal of the input capacitor and output capacitors to the system ground plane. It is preferred to put these vias along the edge of the GND copper closest to the +V copper. These vias connect the input/output filter capacitors to the GND plane, and help reduce parasitic inductances in the input and output current loops.

**Recommendation 6**: AVIN is the power supply for the small-signal control circuits. It should be connected to the input voltage at a quiet point. In Figure 8 this connection is made at the input capacitor.

**Recommendation 7**: Follow all the layout recommendations as close as possible to optimize performance. Not following layout recommendations can complicate designs and create anomalies different than the expected operation of the product.

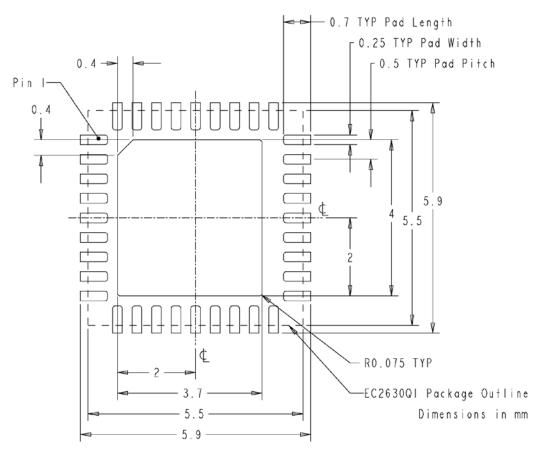

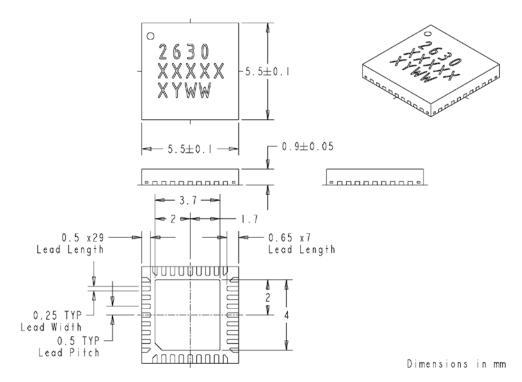

# Package and Mechanical

Figure 10. Recommended PCB footprint

# Mechanical Information

Figure 11. EC2630 Package Dimensions

Packing and Marking Information: <a href="https://www.altera.com/support/reliability/packing/rel-packing-and-marking.html">www.altera.com/support/reliability/packing/rel-packing-and-marking.html</a>

## **Revision History**

| Rev | Date      | Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α   | July 2011 | Introductory production datasheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| В   | Sep 2013  | Formatting changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| C   | May 2016  | <ul> <li>Added solution size</li> <li>Modified description of SYNC_O pin (removed frequency scaling)</li> <li>Modified description of VBOOT pin (added Cboot recommendation)</li> <li>VOUT_OK pin changed to NC. VIN_OK is used for sequencing downstream parts</li> <li>ENABLE pin changed to PVIN (ensures part is always enable when powered)</li> <li>VIN range changed to 10V - 13.2V with typ at 12.</li> <li>Added VOUT min and max limits (as a percentage of Vin)</li> <li>Added data on VIN_OK threshold limits</li> <li>Added more characteristic curves (Vout vs lout at various Vin, ripple, transients, parallel current share, etc)</li> <li>Modified discussion on Frequency sync.</li> <li>Added curves relating Cout/Cfly ratio to Outptut voltage over load and frequency</li> <li>Modified application diagram to remove ENABLE, and modified ENABLE connections of downstream devices</li> <li>Added VIN_OK pull-up resistor recommendation</li> <li>Added application schematic and note on parallel operation</li> <li>Added note to say that only Enpirion PoLs should be used for downstream devices and only other EC2630Qis should be used as parallel devices.</li> <li>Removed external circuitry recommendations for OCP</li> <li>Removed note to contact applications for support</li> <li>Overall formatting changes to the document</li> </ul> |

# Contact Information

Altera Corporation 101 Innovation Drive San Jose, CA 95134 Phone: 408-544-7000

www.altera.com

© 2016 Altera Corporation—Confidential. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.